Faculty of Information Technology

## Master of Computing

## Reducing Test Power for Embedded Memories

Prepared By

Ahmed Awad

Supervised By

Dr.Abdellatif Abu-Issa

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF COMPUTING

### BIRZEIT

June, 2011

#### Acknowledgement

I would like to acknowledge and extend my heartfelt gratitude to all those who helped and supported me to complete my thesis. I'm deeply indebted to my supervisor Dr.Abdellatif Abu-Issa for his help, support and continuous encourage for me. Also, special thanks to the committee of my master thesis defense, Dr.Emad Hamadeh and Dr.Khaled Faraj for their comments to have a high quality thesis. I want also to thank Dr.Said Hamdoui from Delft University in Netherlands for his guidance during working on conference papers. Most special thanks to my father and mother for their support and constant prayers and my family and all my friends who love and encourage me. Thank you all.

## **Table of Contents**

| List of Figures                                                        | IV   |

|------------------------------------------------------------------------|------|

| List of Tables                                                         | V    |

| List of Abbreviations                                                  | VI   |

| Abstract                                                               | VII  |

| المستخلص                                                               | VIII |

| Chapter 1: Introduction                                                | 1    |

| 1.1 SRAM Structure and Functionality                                   | 2    |

| 1.2 SRAM Fault Models                                                  | 6    |

| 1.3 Memory Testing Concepts                                            | 9    |

| 1.4 Memory Testing Algorithms                                          | 12   |

| 1.5 Power Dissipation in SRAM Testing                                  | 15   |

| 1.6 Motivation for SRAM Test Power Reduction                           | 17   |

| 1.7 Thesis Organization                                                | 18   |

| Chapter 2: Related Work                                                | 19   |

| 2.1 Single Bit Change (SBC) in Address Decoder                         | 19   |

| 2.2 Minimizing Test Power Through Reduction of Pre-Charge Activity     | 21   |

| 2.3 March Tests Sequence Reordering Using Genetic Algorithm            | 22   |

| 2.4 Generating Low Power March Tests Using Particle Swarm Optimization | 23   |

| 2.5 Skew Scheme                                                        | 25   |

| 2.6 Power Constrained Embedded Memory BISTArchitecture                 | 26   |

| 2.7 Contribution of The Work Presented In This Thesis                  | 28   |

| Chapter 3: Low Power Zero-One Testing                                  | 29   |

| 3.1 Overview                                                           | 29   |

| 3.2 MBIST Architecture and Address Generators                          | 30   |

| 3.2.1 Bit-Swapping Lfsr (BS-LFSR)                                      | 31   |

| 3.2.2 Dual Speed Lfsr (DS-LFSR)                                        | 32   |

| 3.2.3 Bipartite LFSR                                                   | 33   |

| 3.3 Detecting Stuck-At Fault Patterns                                  | 34   |

| 3.4 Simulations and Experimental Results                               | 35   |

| 3.4.1 Code Description                                                 | 36   |

| 3.4.2 MBIST Simulation                                                 | 36   |

| 3.4.3 Address Generators Simulations and Results                       | 37   |

| 3.4.4 Testing Patterns Simulations and Results                         | 39   |

| 3.5 Summary                                                            | 40   |

| Chapter 4: Low Power March Tests                                       | 41   |

| 4.1 Overview                                                           | 41   |

| 4.2 Modified March C- Algorithm                                        | 42   |

| 4.3 Implementation                                                     | 44   |

| 4.4 Fault Coverage                                                     | 45   |

| 4.5 Experimental Results                                               | 47   |

| 47          |

|-------------|

| 47          |

| 49          |

| emories .50 |

| 50          |

| 51          |

| 53          |

| 56          |

| 57          |

| 59          |

| 60          |

| 60          |

| 61          |

| 62          |

| 67          |

| 69          |

| 70          |

| 71          |

|             |

## List of Figures

| Figure 1.1: Memory Pyramid                                                         |     |

|------------------------------------------------------------------------------------|-----|

| Figure 1.2: Increased number of SRAMs in SoC                                       | 3   |

| Figure 1.3: 6T SRAM cell                                                           |     |

| Figure 1.4: SRAM Connections                                                       | 5   |

| Figure 1.5: SRAM cell during Read 1 Operation                                      |     |

| Figure 1.6: SRAM cell during Write 0 Operation                                     |     |

| Figure 1.7: Stuck-at 0 cell State Diagram                                          |     |

| Figure 1.8: Address Decoder Fault                                                  |     |

| Figure 1.9: Transition Fault State Diagram                                         |     |

| Figure 1.10: Coupling Fault State Diagram                                          |     |

| Figure 1.11: Memory Testing Pattern                                                |     |

| Figure 1.12: MBIST Architecture                                                    |     |

| Figure 1.13: 3-bit LFSR                                                            |     |

| Figure 1.14: Symbols Used in Memory Testing Algorithms                             |     |

| Figure 1.15: Zero-One Algorithm                                                    |     |

| Figure 1.16: March C- Algorithm                                                    |     |

| Figure 1.17: First two Elements of March C-                                        |     |

| Figure 1.18: CMOS Logic                                                            |     |

| Figure 2.1: Modified Pre-charging Circuitry                                        |     |

| Figure 2.2: Switching Activity in March C- Algorithm                               |     |

| Figure 2.3: PSO Particle Structure                                                 |     |

| Figure 2.4: Applying element M1 of March C- on two SRAMs                           |     |

| Figure 2.5: Skew Scheme                                                            |     |

| Figure 2.6: Power-Constrained MBIST Architecture                                   |     |

| Figure 2.7: Wrapper Address Generator                                              |     |

| Figure 3.1: Used MBIST Architecture                                                |     |

| Figure 3.2: BS-LFSR                                                                |     |

| Figure 3.3: DS-LFSR                                                                |     |

| Figure 3.4: Intermediate Pattern Generation in Bipartite LFSR                      |     |

| Figure 3.5: Bipartite LFSR Architecture                                            |     |

| Figure 3.6: Fault Free Memory Simulation                                           |     |

| Figure 4.1: March C- Algorithm                                                     |     |

| Figure 4.2: Modified March C- Algorithm                                            |     |

| Figure 4.3: Tri-State Buffers for 4-bit word                                       |     |

| Figure 4.4: Transitions of two vertically neighbored cells in March C              |     |

| Figure 4.5: States of two vertically Neighbored Cells in Modified March C-         |     |

| Figure 4.6: States of two horizontally neighbored cells in Modified March C        |     |

| Figure 4.7: Expanded March C- Algorithm                                            |     |

| Figure 4.8: States of two vertically neighbored cells in Expanded Test             |     |

| Figure 4.9: Transitions of two horizontally neighbored even cells in Expanded Test |     |

| Figure 5.1: One-Stage Scheme                                                       |     |

| Figure 5.2: Two-Stage Clustering                                                   |     |

| Figure 5.3: Multi-Stage Scheme                                                     |     |

| Figure 5.5: Multi-Stage Scheme<br>Figure 5.4: Architecture of Low Routing MBIST    |     |

| Figure B.1: Crossover Operation                                                    |     |

| Figure D.1: Maximal Length LFSR                                                    |     |

| 1 นารณร D.1. พลงแกล Lรแรน LISK                                                     | / 1 |

## List of Tables

| Table 2.1: SBC in Address Decoder                                           | 20 |

|-----------------------------------------------------------------------------|----|

| Table 2.2: New Generated March Tests using Genetic Algorithm                | 23 |

| Table 2.3: New March Tests Based on PSO Scheme                              | 25 |

| Table 3.1: Normal and BS- LFSR Vectors                                      | 32 |

| Table 3.2: Switching Activity for Address Generators with Seed "11111"      | 38 |

| Table 3.3: Switching Activity for Address Generators with Seed "010101"     | 38 |

| Table 3.4: Address and Data Bus Switching Activities for Different Patterns | 39 |

| Table 4.1: Power results of normal, modified and expanded March C- Tests    | 49 |

| Table 5.1: Used Memory Configurations                                       | 57 |

| Table 5.2: Peak Power and Testing Time for Different Schemes                | 58 |

| Table 5.3: Combining One-Stage Scheme with Modified March C- Algorithm      | 59 |

| Table A.1: Fault Primitives                                                 | 67 |

| Table A.2:Some March Tests with their Fault Coverages                       | 68 |

| Table D.1: Maximal Length LFSRs                                             | 71 |

|                                                                             |    |

#### **List of Abbreviations**

- 1T : One Transistor Technology

- 6T : Six Transistor Technology

- ATE : Automatic Test Equipment

- BIST : Built-in Self Test

- BL : Bit Line

- BLB : Bit Line Complement

- BS-LFSR : Bit-Swapping LFSR

- CMOS : Complementary Metal Oxide Semiconductor

- CUT : Circuit Under Testing

- DRAM : Dynamic Random Access Memory

- DRDF : Deceptive Read Destructive Fault

- DS-LFSR : Dual-Speed LFSR

- IRF : Incorrect Read Fault

- LFSR : Linear Feedback Shift Register

- MBIST : Memory Built-in Self Test

- MUT : Memory Under Testing

- NOP : Number Of Operations

- PSO : Particle Swarm Optimization

- RDF : Read Destructive Fault

- RES : Read Equivalent Stress

- SA : Switching Activity

- SAIF : Switching Activity Interoperation Function

- SBC : Single Bit Change

- SoC : System on Chip

- SRAM : Static Random Access Memory

- TPG : Test Pattern Generator

- VLSI : Very Large Scale Integration

- WDF : Write Disturb Fault

- WL : Word Line

#### Abstract

With the increased number of embedded memories in mobile devices, minimizing the test power becomes a serious concern, especially when parallel testing is applied. Battery will be lost and the entire System on Chip (SoC) is subjected to be damaged if the consumed power exceeds the power constraint of the chip.

This dissertation proposes a number of techniques to address these challenges during memory testing. The first technique is based on using low power Linear Feedback Shift Register (LFSR) as an address generator when applying Zero-One algorithm during Memory Built-in Self Test (MBIST), and then, re-order the test so that total switching activity in address decoder and write driver is minimized. The obtained results show that up to 60% reduction in switching activity can be achieved during testing large size memories with negligible overhead in hardware area.

Another technique that aims to reduce average and peak power during March tests is proposed. In this technique, the word of the Memory Under Testing (MUT) is divided into two clusters so that write operation is applied just to one cluster. Obtained results show that around 42% reduction in peak power and around 35% reduction in average power can be achieved using the proposed technique with the same fault coverage and testing time of original tests.

Finally, a new scheme is proposed to manage parallel testing of large number of embedded memories in SoC. This scheme is based on grouping different memories into clusters based on their word lengths and scheduling read and write operations in such a way that the consumed power is optimal. Simulation results of case-of-study show that up to 60% reduction in peak power can be achieved in case of parallel testing at a cost of only one additional clock cycle in testing time

المستخلص

مع التزايد المستمر في عدد الذاكرات المستعملة في الأجهزة المتنقلة، تقليل القدرة المستهلكة عند فحص هذه الذاكرات أصبح تحديا هاما، خصوصا عند تطبيق الفحص المتوازي على هذه الذاكرات. طاقة البطارية سوف تستنزف والنظام على القطعة الإلكتروني ة بكامله معرض للتلف في حال تجاوزت القدرة المستهلكة الحد المسموح.

تعرض هذه الرسالة عددا من الطرق لمواجهة مشكلة القدرة المستهلكة أثناء فحض الذاكرة. تعتمد الطريقة الأولى على استعمال مولد للعناوين ذو طاقة قليلة أثناء استعمال طريقة صفر -واحد في فحص الذاكرة، ثم تقوم هذه الطريقة على إعادة ترتيب الفحص بطريقة تقلل التغيرات في القيم الرقمية إلى الحد الأدنى. وقد أثبتت النتائج يمكن حفظ حوالي 60% من القدرة المستعملة باستخدام هذه الطريقة مع زيادة لا تذكر في المساحة في القطعة الالكترونيق.

تعتمد الطريقة الثانية على تقليل القدرة المتوسطة والقدرة القصوى إثناء استعمال الفحص الشامل للذاكرة لكشف أنواع كثيرة من الأعطاب. يتم ذلك بواسطة تقسيم الخلايا في كل عنوان في الذاكرة كل مجموعتين، ومن ثم القيام بعملية الكتابة فقط على مجوعة واحدة من تلك المجموعات. وقد أثبتت النتائج انه يمكن حفظ حوالي 42% من القدرة القصوى وحوالي 32% من القدرة المتوسطة باستخدام هذه الطريقة مع كشف نفس الأنواع من الأخطاء وفي نفس زمن الفحص

وأخيرا، تقوم الطريقة الثالثة على تقليل القدرة القصوى المستهلكة عند فحص عدد كبير من الذاكرات بالتوازي. وتقوم هذه الطريقة على توزيع الذاكرات في مجموعات بناء على أحجامهم ومن ثم جدولة عمليات القراءة والكتابة بطريقة تقلل القدرة القصوى إلى الحد الأدنى. النتائج أثبتت أنه يمكن حفظ أكثر من 60% من القدرة القصوى مع زيادة مهملة في وقت الفحص.

## CHAPTER 1

#### Introduction

With the advances in Very Large Scale Integration (VLSI) technology, more and more contents are integrated together in System on Chip (SoC).Semiconductor embedded memories can be considered as the densest circuitry and it is expected that in 2014, embedded memories will occupy around 94% of silicon area in the SoC [1]. Due to their high density and intensive access, embedded memories are more likely to be affected by manufacturing faults rather than other components in the chip. Hence, memories have to be tested effectively [2].

Due to its high speed and reliability, Static Random Access Memory (SRAM) is more commonly used in different applications such as digital cameras and mobile phones, for this reason, many techniques were developed for testing embedded SRAMs [3]. The increased number of embedded memories in SoC makes testing process more complex in terms of time and power [4]. Testing power plays an important role in evaluating the effectiveness of the test. If the power consumed exceeds the accepted power constraint, then the chip is subjected to structural degradation and may be damaged [5].

This thesis addresses the problem of power consumption during testing SRAM for the existence of manufacturing faults. It studies the existing algorithms for memory testing and provides an enhancement for some of those techniques so that testing power is reduced with the same fault coverage and within an accepted testing time. The main objectives of this dissertation are:

1. To reduce testing power of Zero-One algorithm that is used for testing embedded memories of personal applications such as digital cameras.

- 2. To reduce testing power of March tests that are used for intensive testing of embedded memories used in critical fields such as military applications.

- 3. To reduce peak power when parallel testing is applied for a large number of embedded memories in SoC.

This chapter introduces the main concepts about SRAM testing and manufacturing faults. Then it addresses memory testing patterns and the main sources for power dissipation during testing. Finally, the motivation of this dissertation and its general organization are summarized.

#### **1.1 SRAM Structure and Functionality**

SRAM is a volatile memory that is used to store binary values in computer systems. It stores each bit effectively using a latching circuit which is made of transistors. It loses its data when its power supply is turned off [6].

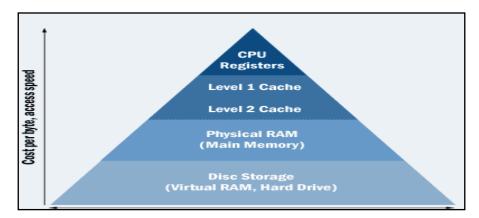

SRAM is faster than Dynamic Random Access Memory (DRAM) since no refreshment is required for its functionality. Actually, SRAM was found to reduce the gap in speed between Microprocessor Unit (MU) and the main memory in which DRAM is used. Thus, SRAM is used in the cache memory of computer. More than one level of cache may be required [7]. Figure 1.1 shows the memory pyramid which proves that memory was the driving factor behind the rapid development in Complementary Metal Oxide Semiconductor (CMOS) technology [8].

SRAM consumes less power than DRAM since DRAM refresh current is much higher than SRAM standby current. Also, it is more reliable than DRAM. Due to those advantages, SRAM is commonly used as an embedded memory in small and portable devices such as mobile phones and digital cameras. Also it is widely used in the buffers of routers and switches in the network. LCD screens and printers use SRAM to hold image that has to be displayed or printed [9].

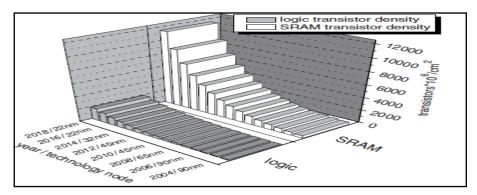

The main disadvantage of SRAM is its high cost and the large area it occupies in SoC .Thus, large number of small SRAM memories is used in SoC instead of using large size ones .According to Moores' Law, the number of components on chip doubles every 18 months. Thus, the number of embedded SRAMs in SoC increases rapidly with time. Figure 1.2 shows how the number of SRAMs in SoC increases if compared with other logic on chip [11].

Figure 1.1: Memory Pyramid [10]

Figure 1.2: Increased number of SRAMs in SoC [11]

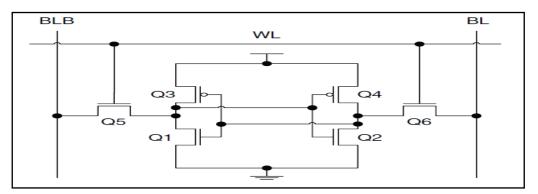

SRAM consists of a number of cells; each cell stores a binary value. There are several technologies for SRAM cells. To reduce the area occupied by embedded memories, one transistor (1T) technology, in which the cell consists of one transistor surrounded by intelligent control circuitry, was found and recently some companies have started to use this technology in the design of SoC [12]. However, six transistors (6T) SRAM cell is still the dominant technology used due to its reliability and stability and it is still considered in researches of test power, hence, it will be considered in this dissertation. As shown in figure 1.3, 6T cell consists of 4 transistors that forms two crossed coupled inverters to store the binary value. Two access transistors (Q5 and Q6) connect or disconnect the cell to the bit lines (BL, BLB). [13].

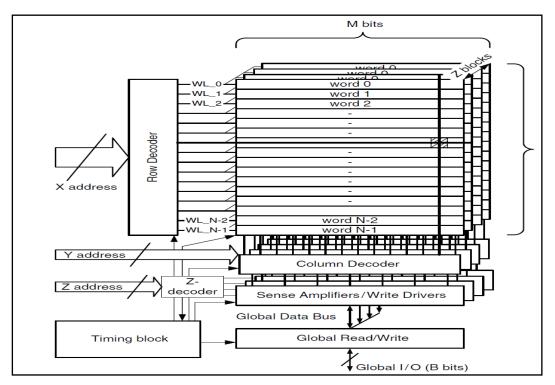

Usually, SRAM consists of a number of locations, according to the number of cells in each location; SRAM can be classified in two main types [14]:

- 1. Bit Oriented SRAM which contains only one cell in each memory location.

- 2. Word Oriented SRAM: In which each location contains a number of cells based on the word length. For example, if the word is 8 bit, then each memory

location contains 8 cells. Most of the memories used in SoC are word oriented ones with word lengths vary between 32-512 bits and 640bits in some cases such as video applications [15].

Figure 1.3: 6T SRAM cell [13]

SRAM is accessed by applying read and write operations on its cells. In case of read operation, the current value of the cell is retrieved whereas a new value is applied to this cell during write operation. Usually, address decoder is used to select the memory location that will be accessed. Then, the word line for that location is asserted so that the required cell is connected to the bit lines through access transistors. A control signal is used to determine whether the operation applied is read or write. In case of write operation, the value in the data bus is written to the cell. Some peripheral devices are required such as write driver which pulls down one of the bit lines so that the value in the data bus to be written is applied on the bit lines, and the sense amplifier that amplifies the small analog differential voltage developed on the bit lines by read operation to full swing digital output [13]. Figure 1.4 shows SRAM with its peripheral devices.

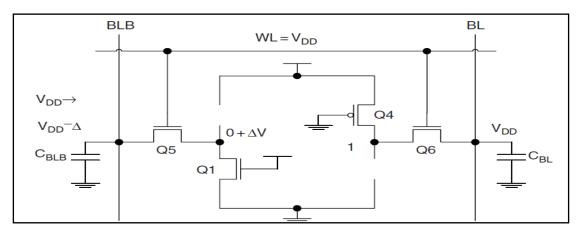

To apply a read operation, both bit lines are first pre-charged to Vdd. Then, the word line for the word that has to be accessed is asserted. By this way, the gate of the two access transistors (Q5 and Q6) is connected to logic 1. Consequently, both access transistors are ON and connect the cell to the two bit lines. If the cell contains logic 1, BL remains in its pre-charging level while BLB is discharged through transistors Q5 and Q1 that form a voltage divider whose output is no longer 0 and it is connected to the input of inverter Q2-Q4. In general  $0+\Delta V$  should not exceed the switching threshold of the inverter Q2-Q4. Figure 1.5 illustrates a simplified model of 6T cell during read 1 operation. If the cell contains 0, BL will be discharged through

transistors Q6 and Q2 while BLB will remain in its pre-charging level, then the same operations will be applied [11].

Figure 1.4: SRAM Connections [11]

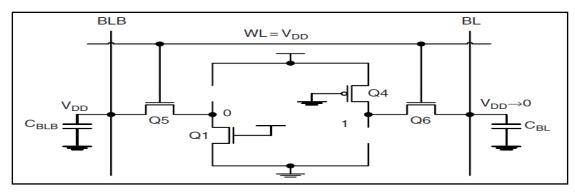

In case of write operation, both bit lines are pre-charged to Vdd, then, one of those bit lines is pulled down through the strong write driver so that the value that has to be written is applied on both bit lines. In general, during write operation, the bit lines are driven by strong write driver to ensure overriding the current value that the cell holds. Thus, the write current is much higher than read current. Figure 1.6 shows a simplified model for SRAM cell when write 0 operation is applied [11].

Figure 1.5: SRAM Cell during Read 1 Operation [11]

Figure 1.6: SRAM Cell during Write 0 Operation [11]

#### **1.2 SRAM Fault Models**

A fault model is a description about how the components of a faulty circuit will behave [16]. Due to the high density and intensive access of embedded SRAM instances in SoC, they are more likely to be affected by manufacturing faults that may affect the functionality of the system. The number of memory faults is more than that for any other component in SoC, for this reason several fault models were dedicated in order to detect these faults. [17]

SRAM faults can be classified in two main categories:

- **A. Single –cell Fault**: A fault that involves only one cell in the memory, this includes the following faults:

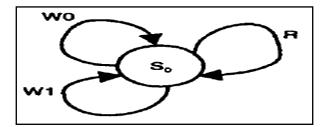

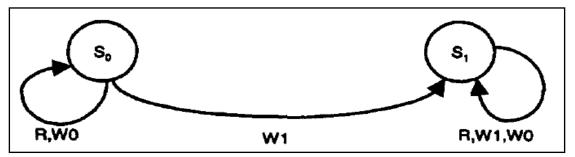

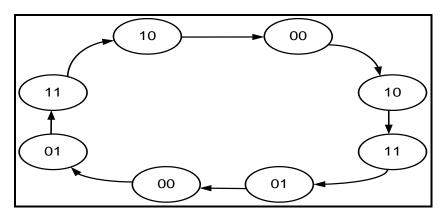

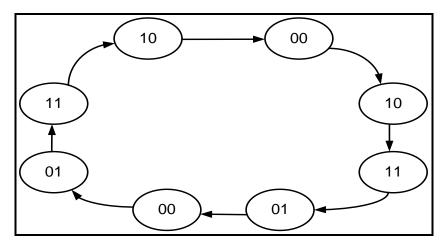

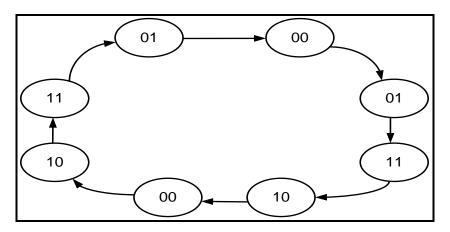

- Stuck-At fault: It is the most common type of faults in SRAM cells. In this fault, the cell value is stuck-at 0 or stuck-at 1 so that it cannot be overwritten by the complementary value. Typically, memories of personal devices such as mobile phones are tested mainly for this type of faults. Stuck-at faults can be caused by several reasons, such as short circuits in the connections and transistor defects. Figure 1.7 shows the state diagram of a stuck-at 0 cell. W0 and W1 represents write 0 and write 1 operation respectively while R means a read operation. S represents the current value of the cell [18].

- 2. Stuck open fault: In this type of faults, the cell cannot be accessed due to open word line or open bit line [19].

- 3. Address decoder fault: This type of faults can be classified under the stuck-at faults since one of the nodes in the address decoder may stuck

at 0 or 1 leading to accessing wrong address, no address, or multiple addresses. Figure 1.8 illustrates this type of faults [20].

Figure 1.7: Stuck-at 0 cell State Diagram [18]

Figure 1.8: Address Decoder Fault [20]

4 Transition fault: In this type of faults, if the cell moves from one state to another, it cannot move back to the pervious state. For example, if 1 was written to a cell that contains 0, then 0 was written again, the cell state will remain 1. This type of faults can be caused by the absence of access transistors. Figure 1.9 shows the state diagram of this type of faults [18].

Figure 1.9: Transition Fault State Diagram [18]

5. Write Disturb Fault (WDF): In this fault, a non transition write operation will cause the cell to go into erroneous state. For example, if a cell contains 0 and 0 was written to it, then its state will be 1 [21].

- 6. Read Destructive Fault (RDF): The read operation in this fault will cause the cell to go into erroneous state. The result of read operation will be wrong [21]

- 7. Deceptive Read Destructive Fault (DRDF): This type of fault is the same as RDF but it is more difficult to detect since read operation result will be correct but the state of the cell will be wrong after this read operation [21].

- 8. Incorrect Read Fault (IRF): In this fault, the state of the cell will not be changed during the read operation, but the read result will be wrong [21].

- **B. Two-Cell Fault:** A fault that involves two cells. This includes the following types of faults [22]:

- 1. Inversion coupling fault: In this type of faults, if the value of a cell is changed, then its neighbor will go into erroneous state. Usually the first cell is called **aggressor cell** whereas the affected cell is called **victim cell**. This fault could be symmetric; in which the victim cell state will go from high to low or from low to high following the aggressor cell transitions or it could be asymmetric so that the victim cell moves into one transition only. Also this fault could be one-way, in which the fault is sensitized by high to low or low to high transition or two-way which is sensitized in both transitions in the aggressor cell. Figure 1.10 shows the state diagram for a pair of cells with inversion coupling fault.

- 2. State coupling fault: Within this fault, the state of the aggressor cell will cause the victim cell to be affected by any of the previously mentioned single-cell faults. For example, if the aggressor cell state is 0, then the victim cell may be affected by transition fault.

- **C. Other faults:** There are other types of faults such as delay related faults, stability faults and data retention faults. These types of faults are usually ignored in normal applications but have to be detected in applications that contain critical data in which memory has to be intensively accessed [23].

Figure 1.10: Coupling Fault State Diagram [18]

#### **1.3 Memory Testing Concepts**

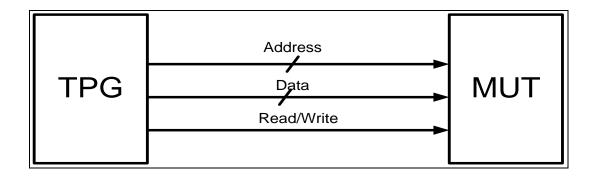

SRAM has to be tested for the existence of manufacturing faults since these faults will affect the functionality of the memory. Testing phase means applying a set of patterns generated from a Test Pattern Generator (TPG) to the Memory Under Testing (MUT) and then comparing the obtained result with the expected result in case of fault free memory. **Testing pattern** consists of three parts as shown in figure 1.11 [24]:

- 1. The address that has to be accessed.

- 2. The data that will be written in case of write operation.

- 3. The control signal that determines whether a read or write operation has to be applied.

Figure 1.11: Memory Testing Pattern

Usually testing is performed either during manufacturing or during application. In general, testing is classified in two types:

- External Testing: In this type of testing, an external instrumentation is used for generating testing patterns that are applied to the MUT. The equipment used is called Automatic Test Equipment (ATE). The main problem with this type of testing is its cost which is proportional to the number of pins of the MUT. Another disadvantage is the large testing time required since the SoC consists of hundreds of embedded memories that will be tested sequentially using a single ATE [25].

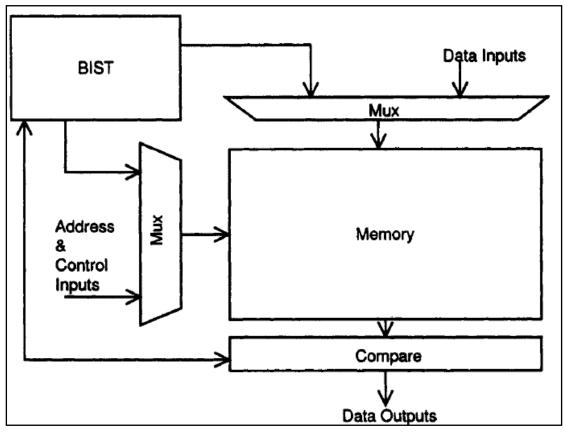

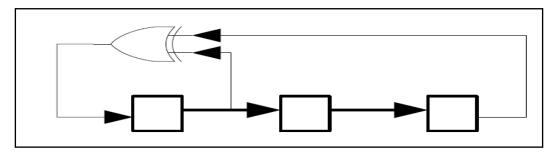

- 2. Built-in Self Test (BIST): this type is the most commonly used in testing memories. In Memory BIST (MBIST), a TPG is built in the chip that contains the MUT so that the memory is tested without any communication with the external world. BIST was found to overcome the problems of the external testing such as the high cost and the testing time. By using BIST, multiple embedded memories in SoC can be tested in parallel so that testing time is reduced. Figure 1.12 shows the main components of MBIST [26] which are:

- 1. BIST engine that generates the pattern (address, data, and control) that will be applied to MUT.

- 2. MUT that has to be tested for faults.

- 3. Comparator that is used to compare the results read from MUT with the expected result so that a pass/fail indication is generated.

4. Multiplexers whose selection line is the testing mode signal to determine whether the system is in the testing mode or in the normal mode. If the system is in the testing mode, then the pattern generated by the BIST engine will be applied to the memory, otherwise, the data coming from microprocessor will be the input of memory.

Figure 1.12: MBIST Architecture [18]

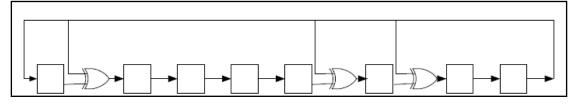

BIST engine consists of two parts which are: the address generator and the controller. The address generator generates the address that has to be accessed. Usually a counter is used as an address generator, but this will result in large overhead in the hardware area, thus, Linear Feedback Shift Register (LFSR) is sometimes used instead of the counter due to its low overhead in the hardware area [27]. LFSR is a register that consists of a number of flip flops and an XOR gate that is located based on the characteristic polynomial. It can be considered as a source of binary pseudorandom test sequences that can be used in testing combinational circuits and also as an address generator in memory testing. LFSR can be maximal length if it generates all the possible testing vectors (except the 0's vector since it blocks the 1.13 LFSR). Figure shows 3-bit LFSR with characteristic polynomial  $p(x) = x^3 + x + 1$ . Usually LFSR starts generating the addresses with a seed value, for example, if the seed for the LFSR shown in figure 1.13 is 111, then the sequence of addresses generated will be {111,011,101,010,001,100,110.111}. A simple circuit can be added to generate the 000 address [28].

Figure 1.13: 3-bit LFSR

The controller in BIST engine is responsible for generating data and control signals that will be applied on the memory location generated by address generator. Usually the controller is based on finite state machine while generating its patterns [29].

BIST schemes are classified in two main types [28]:

- Test per clock, in which BIST engine generates a pattern to be applied to the Circuit Under Testing (CUT) per clock.

- 2. Test per scan, in which the storage elements in the CUT are transformed into scan cells that are connected to each other forming a scan chain. Then, the testing vectors and responses are shifted through this chain. Usually this scheme is used for testing complex sequential circuits since it doesn't require large overhead area, but it results in large testing time.

Usually in memory testing, test per clock scheme is used due to its low testing time and there is no need for forming scan chains in testing memories since memory structure is the same for all memories.

#### **1.4 Memory Testing Algorithms**

Many algorithms were developed for testing memory. Fault coverage, which is defined as the number of detected faults divided by total number of faults, was considered as the superior factor in evaluating any memory testing algorithm. With the increased number of embedded memories in the SoC, **testing time** became another important factor in testing. To reduce the testing time, parallel testing can be considered as a good solution, but this will result in excessive **test power** since multiple memory instances will be tested simultaneously. Hence, the power consumed during the testing mode could be much higher than that in the normal mode since in the testing mode multiple memories will be tested concurrently whereas some memories will be idle during the functional mode [30].

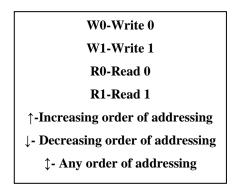

A memory testing algorithm consists of a sequence of read and write operations that will be applied on a sequence of addresses in the memory. In each read operation, the results read from MUT are compared with the expected read result to detect any faults in memory [31]. The following provides a brief description about the most commonly used memory testing algorithms. Figure 1.14 defines the symbols used in all memory testing algorithms:

Figure 1.14: Symbols Used in Memory Testing Algorithms

1. Zero-One algorithm: This algorithm is used to detect only stuck-at faults in MUT. It is commonly used in personal and portable devices such as mobile phones. Also it is used when embedded memories of those devices are being tested during the application not only during manufacturing. As shown in figure 1.15, simply a 0 is written to all memory addresses, then it is read from those locations in order to detect stuck-at 1 cells. Then, 1 is written to all memory locations then it is read in order to detect stuck-at 0 cells. Note that the testing time of this algorithm is 4n where n is the number of addresses of the MUT. Thus, this algorithm belongs to O(n) testing algorithms [18]

#### $\uparrow$ (W0), $\uparrow$ (R0), $\uparrow$ (W1), $\uparrow$ (R1),

Figure 1.15: Zero-One Algorithm

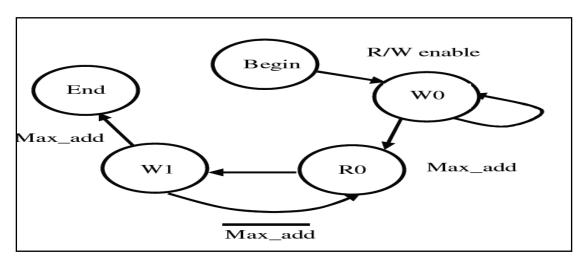

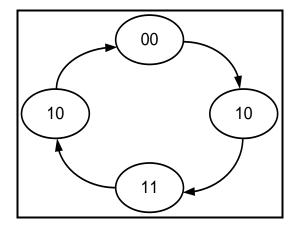

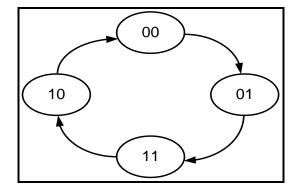

2. March Tests: It was proven that March tests are superior to other memory testing algorithms due to their high fault coverage and low testing time. In general, March algorithms are O(n) tests. They were found in order to detect coupling faults and other types of faults. A March test consists of a number of March elements, each element consists of a sequence of operations that will be applied on all memory addresses based on the given addressing order in the algorithm. Usually these tests are used for testing embedded memories in critical applications such as military applications and others so that the memory has to be intensively tested. One of the commonly used March tests is March C- algorithm which can detect stuck-at faults, transition faults, and inversion coupling faults. Figure 1.16 illustrates March C- algorithm and its main elements (M0, M1 ...,M5) [32].

| <b>↓ (W0);</b> ↑ ( | (R0,W1); | ↑ (R1 ,W0);↓     | (R0,W1);  | ↓( <b>R1,W0</b> ); | \$ (R0) |  |

|--------------------|----------|------------------|-----------|--------------------|---------|--|

| MO                 | M1       | M2               | M3        | M4                 | M5      |  |

|                    | Figure 1 | 1.16: March C- A | Algorithm |                    |         |  |

March C- algorithm contains increasing and decreasing orders of addresses in order to detect the coupling faults when the aggressor cell address is greater than the address of the victim cell (a > v) and when the aggressor cell address is lower than the victim cell address (a < v). Other March tests were developed in order to increase the fault coverage. For example, March C- algorithm cannot detect DRDFs, thus, March SS was found to detect this type and also other types of faults. Other March algorithms were found to detect and identify the location of the faults, such as March DSS. Those algorithms are called **diagnosis March Tests** [33]. More about March tests can be found in appendix A.

Zero-One and March algorithms are not the only algorithms developed for memory testing, other algorithms were found such as Walking 1/0 and GALPAT. Those algorithms have a good fault coverage but their complexity are  $O(n^2)$  and  $O(n^{3/2})$  respectively. Thus, a large testing time is needed [33].

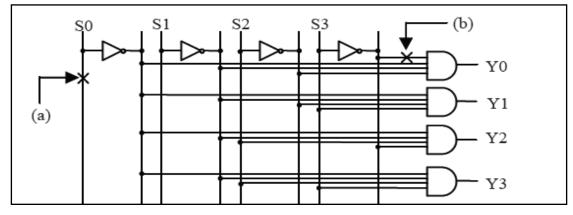

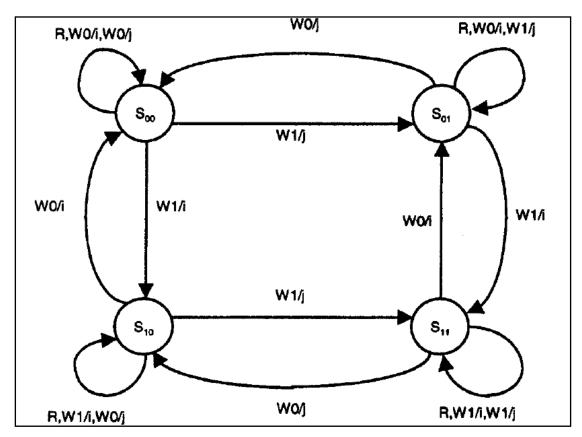

Memory testing algorithms are implemented as a finite state machine which is executed by the controller in the BIST engine [29]. Figure 1.17 shows a finite state machine implementing the first two elements in March C- algorithm.

Figure 1.17: First two Elements of March C- [29]

#### **1.5 Power Dissipation in SRAM Testing**

Before considering power dissipation during SRAM testing, the following terminology has to be considered [28]:

1. Average Power: The total energy consumed divided by testing time.

- 2. Instantaneous Power: The power dissipated at any instant of time.

- 3. Peak Power: The maximum instantaneous power.

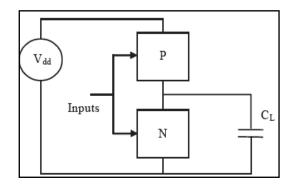

In CMOS technology, power dissipation can be classified in two types [30]:

1. Static power dissipation which is caused by leakage current. In general, leakage current increases when more and more transistors are squeezed onto a chip since when the transistor becomes smaller, the insulating layer becomes thinner causing more and more leakage current. In general, in CMOS technology, static power is low if compared with other technologies.

2. Dynamic power dissipation which is caused by charging and discharging of load capacitance (C<sub>L</sub>) of the transistors. Figure 1.18 shows the general model of CMOS node. When a transition from low to high occurs, then the capacitor will be charged to Vdd with charge Q= C<sub>L</sub>Vdd. So the energy consumed= QVdd= C<sub>L</sub>(Vdd)<sup>2</sup>. Since the load capacitor will save (1/2) C<sub>L</sub>(Vdd)<sup>2</sup>. The other half will be dissipated as

heat in the pull up network (P). In case of discharging, the load capacitor will discharge all the energy that is has and this energy cannot enter the ground rail since Q.Vdd=Q.0=0. Thus,  $(1/2) C_L(Vdd)^2$  will be dissipated as heat in the pull down network (N). By this way, in any node, the dynamic power dissipated can be defined in (1.1).

#### $Pdyn = ((1/2) * CL * Vdd^2 * N)/T$ (1.1)

Where CL is the load capacitance of the transistor and Vdd is the biasing voltage, N is the total number of transitions in the node, and T is the testing time. Usually any transition is called **Switching Activity** (**SA**). Note that power dissipation is the same for up and down transitions if assuming the same sizing of P and N transistors. [30].

Figure 1.18: CMOS Logic [30]

Dynamic power is the dominant source of power dissipation when testing embedded SRAM. Thus, it is the power considered in this dissertation. Actually, dynamic power dissipation during SRAM testing is caused by three main factors [34]:

- 1. High Switching activities in address decoder and data bus.

- 2. Power dissipated in peripheral devices such as sense amplifier.

- 3. Power dissipated in memory array.

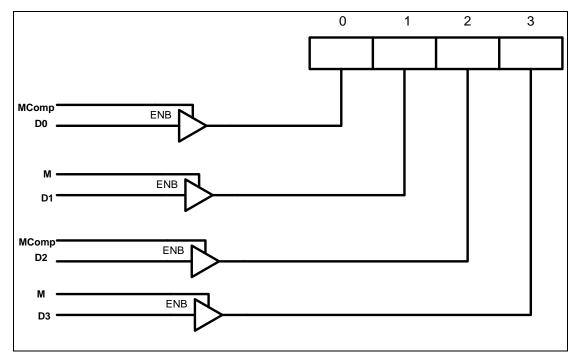

The power consumed in memory array forms the major part of power dissipation during testing. It is caused by read and write operations applied on memory cells. Write current is much higher than the read current since the value of the cell has to be overwritten with new value. Therefore, the voltage swing in write operation is set to Vdd. If write operation has to be performed on one cell in a word, the other cells in this word perform read operations whose results are neglected. These unnecessary read operations are called Read Equivalent Stress (RES).) Read and write drawn currents are represented in (1.2) and (1.3) respectively [35].

$$Idda(r) = [m * Idc(r) * Dt + m * Cd * DV(r)] * f$$

$$(1.2)$$

$$Idda(w) = \{p * [Idc(w) * Dt + Cd * DV(w)] + (m - p) * [Idc(r) * Dt + Cd * DV(r)]\} * f$$

(1.3)

Where m is word length, Idc(r) and Idc(w) represent the DC current on the bit lines during read and write operations respectively, Dt is the assertion period of WL, Cd is the capacitance of the bit line, p is the number of memory on which write operation will be applied, DV(r) and DV(w) represent the voltage swing of the read and write operations respectively, and f is the operation frequency. Note that in general m=p; however, for Bit/byte-Write Enable memories these parameters may be different. It is obvious that when a write operation is performed on a cell in a word, the other cells perform RES whose results will be neglected

#### **1.6 Motivation for SRAM Test Power Reduction**

SRAM testing entails excessive average power dissipation due to the large number of switching activities in address decoder and data bus in addition to the sequence of read and write operations applied during testing. Excessive average power means more heat which will increase the temperature of the chip; consequently, the chip may be damaged [30].

When parallel testing is performed on a number of embedded memories in SoC, there will be concurrent write operations that will result in excessive peak power. If peak power exceeds the power constraint, then the chip may be damaged. Excessive peak power will cause more noise that will erroneously change the logic value of nodes in the chip; hence, the system functionality will be impacted [30].

Although many algorithms were developed for SRAM testing, maximizing the fault coverage was the superior purpose of most of them, and only few of those algorithms focus on reducing the testing power which plays an important role in evaluating the effectiveness of the test. The limited number of techniques in reducing the testing power of SRAM was the main motivation of this dissertation.

#### **1.7 Thesis Organization**

This thesis aims to reduce testing power of Zero-One algorithm which is used for testing embedded SRAMs of personal devices, and to reduce the average and peak power of March tests which are used for intensive testing of embedded SRAMs used in critical applications. The last objective is to reduce the peak power when multiple embedded SRAMs in SoC are being tested in parallel.

In chapter 2, literature on previous work is summarized. This chapter will describe the previous algorithms developed for reducing SRAM testing power and how this dissertation contributes the previous work.

Chapter 3 of this thesis provides an enhancement on Zero-One algorithm to reduce the switching activity in the address decoder by using low power address generators, and reduces the switching activity in the data bus by reordering the algorithm. March tests, which are the most commonly used are modified in chapter 4 so that both the average and peak powers are reduced.

In chapter 5, a new scheme is proposed in order to reduce the peak power when large number of embedded SRAMs in SoC has to be tested in parallel. Finally, chapter 6 concludes this dissertation and describes the future work.

# CHAPTER 2

#### **Related Work**

Due to the large number of faults in embedded SRAMs in SoC, many algorithms were developed in order to detect, and in some cases diagnose, these faults. Most of these algorithms focus on maximizing the fault coverage and reducing testing time. The increased complexity in VLSI technology results in more and more embedded memories in SoC, which has resulted in high power consumption in the chip .Testing power forms a major part of this power dissipation. Nevertheless, only few techniques were dedicated in order to reduce memory testing power.

The main motivation behind reducing testing power of embedded memories is that the power consumed during testing could be twice that in the functional mode since during testing multiple memories will be tested in parallel whereas some memories will be idle in the functional mode [30].

Some techniques in the literature focus on reducing the switching activity during testing in order to reduce the average power while others deal with reducing peak power when multiple embedded memories are being tested in parallel. Maintaining the same fault coverage and low overhead in the hardware area was a challenge in these techniques.

This chapter presents a short survey about previous works in reducing testing power of embedded memories and their shortcomings. Then it reveals the contribution of the work presented in this dissertation.

#### 2.1 Single Bit Change (SBC) in Address Decoder

One of the main sources of power dissipation during testing is high switching activity in address bus since all memory locations have to be tested for faults. Thus, reducing these signal activities will reduce testing power effectively. By this way, original memory testing algorithms have to be reordered so that the switching activity in address bus lines is minimized while retaining the same fault coverage. This is done by using SBC or gray code addressing to ensure that between two successive clock cycles, there will be only one transition. For example, if the MUT has 2 bit address bus, then the sequence of addresses generated during testing will be {00, 01, 11, 10} [30]. Table 2.1 shows how some memory testing algorithms can be modified in order to minimize the switching activity in address decoder. The symbol  $\downarrow_s$  denotes SBC in the addresses generated during testing.

Table 2.1: SBC in Address Decoder [30]

|               | Original Test                                                                                                                                                       | Low-power Test                                                                                                                                                                 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Zero-One      | (W0); (R0); (R1); (R1);                                                                                                                                             | ‡ <sub>s</sub> (W0, R0, W1, R1);                                                                                                                                               |

| Checker Board | $ \begin{array}{c} \uparrow (W(1_{odd}/0_{even})); \uparrow (R(1_{odd}/0_{even})); \\ \uparrow (W(0_{odd}/1_{even})); \uparrow (R(0_{odd}/1_{even})); \end{array} $ | <pre>\$ \$ (W(1<sub>odd</sub>/0<sub>even</sub>),<br/>R(1<sub>odd</sub>/0<sub>even</sub>), W(0<sub>odd</sub>/1<sub>even</sub>),<br/>R(0<sub>odd</sub>/1<sub>even</sub>));</pre> |

It is clear in table 2.1 that Zero-One memory testing algorithm was modified so that the switching activity in address decoder is minimized. This is done by using SBC in the addresses generated and by applying all operations (W0, R0, W1, R1) on each address then moving to the next address instead of applying each operation to all addresses then re-generating all addresses to apply the next operation. Actually, original Zero-One test will cause generating the address sequence four times while they are generated only once in the low power version of this test.

The main drawback of SBC technique is that a modified counter is required in order to generate the required gray code. Actually using normal and gray code counters results in large overhead in the hardware area. In Zero-One testing algorithm, the order of addresses generated is not important, for this reason, it is preferred to use address generators with low hardware area instead of using counters since SoC contains a number of BIST engines and using counter as an address generator for each of those engines will make it costly for BIST in terms of hardware area.

#### 2.2 Minimizing Test Power through Reduction of Pre-charge Activity

Before applying read and write operations in SRAM, the bit lines (BL, BLB) have to be pre-charged to Vdd to ensure applying a correct operation. The precharging circuitries are used for pre-charging and equalizing the high capacitive bit lines. It was proven that the pre-charging circuitry forms around 70% of the power consumed in SRAM [36]

A good methodology is to exploit the predictability of the sequence of addresses generated during testing in order to reduce testing power. Actually, during the functional mode, the next address that has to be accessed cannot be predicted whereas it is known during testing. Hence, all pre-charging circuits for all cells need to remain active in the normal mode whereas during testing mode, just the pre-charging circuits of the cells that have to be accessed will be activated while others can be deactivated [36].

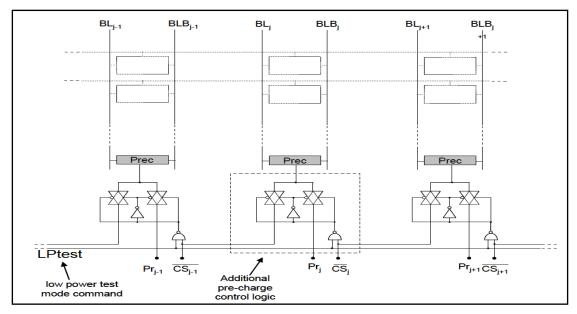

Reducing the pre-charging activity during testing can be implemented by modifying the pre-charging control circuitry in a way that allows choosing a specific cell to be pre-charged. As shown in figure 2.1, a new element has to be added for each column for controlling the pre-charging circuit. This element consists of a multiplexer (which is implemented by two transistors and one inverter) and a NAND gate. The multiplexer has  $LP_{test}$  signal as a selection line in order allow selection between the normal mode and the testing mode. When  $LP_{test}$  signal is activated, then based on the addressing sequence (which is assumed to be word line after word line access), the signal  $CS_j$ ' of column j drives the pre-charging circuitry of the next column j+1 while other cells in the same column are not pre-charged. NAND gate is used to allow the functional mode for a cell when it is selected for read and write operations during testing. Experimental results show that around 50% power reduction was achieved using this technique [36].

The main drawback of this technique is that it supposes word line after word line selection in addressing which is not used by all testing algorithms. In many testing algorithms, read and write operations are applied in parallel to all cells within the same word in order to reduce the testing time. Thus, all pre-charging circuits have to be activated.

Figure 2.1: Modified Pre-charging Circuitry [36]

#### 2.3 March Tests Sequence Reordering using Genetic Algorithm

Since March tests are the most commonly used for intensive testing of embedded memories, it is important to reduce their testing power. Switching activity during testing is the dominant source of power dissipation when applying March tests. This is related to the number of transitions during write operations. For example, in March C- algorithm, the number of transitions is 4 as shown in figure 2.3.

#### $\uparrow (W0);\uparrow (R0, \underline{W1});\uparrow (R1, \underline{W0});\downarrow (R0, \underline{W1});\downarrow (R1, \underline{W0});\uparrow (R0)$

#### Figure 2.2: Switching Activity in March C- Algorithm

One of the used techniques to reduce the switching activity in March tests is to reorder these tests based on genetic algorithm which is usually used for optimization. This algorithm can be used for optimizing between the fault coverage and testing power. For this reason, a cost function was defined based on the fault coverage and test power so that the fault coverage part is maximized, whereas the test power is minimized. The used cost function is represented in (2.1) [37].

Cost(T) = W1 \* (TP(T)/TPmin) + W2 \* (FCmax/FC(T)) (2.1) Where T is a March test that has a fault coverage FC(T) and test power TP(T), TPmin and FCmax represents the minimum test power and maximum fault coverage respectively. W1 and W2 represent the weights assigned to test power and fault coverage. In general the cost for any March test T has to be minimized. The fitness function (F(T)) required for genetic algorithm is 1/Cost(T).

Genetic algorithm is based on starting with initial population, and then a number of genetic operations are applied to generate new populations. Periodically, the fitness function is calculated for each population generated so that population with the maximum fitness function is selected. The initial population for a given March test is the sequence of write operations, for example, the initial population for March C-test is the set {W0, W1, W0, W1, W0}. More about genetic algorithm can be found in appendix B.

This algorithm was applied on March B, March SS and March DSS (which is used for diagnosis) algorithms. Table 2.2 shows the old and newly generated low power March tests based on genetic algorithm.

| March B    | $\{\hat{v}(w0); \hat{v}(r0, w1, r1, w0, w1); \hat{v}(r1, w0, w1); \emptyset(r1, w0, w1, w0); \emptyset(r0, w1, w0)\}$                                                                                                                                                                     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March SS   | $\{\uparrow(w0); \downarrow(r0,r0,w0,r0,w1); \uparrow(r1,r1,w1,r1,w0); \downarrow(r0,r0,w0,r0,w1); \downarrow(r1,r1,w1,r1,w0); \uparrow(r0) \}$                                                                                                                                           |

| March DSS  | { (m, w0); (m, r0, w0, r0, w1); (m, r1, w1, r1, w0); (m, w0, r0, w1); (m, r1, w1, r1, w0, w0,                                                                                                                                                                                             |

|            | r0); <sup>1</sup> / <sub>2</sub> (r0, w0, r0); <sup>1</sup> / <sub>2</sub> (r0, w1, r1); <sup>1</sup> / <sub>2</sub> (r1, w1); <sup>1</sup> / <sub>3</sub> (r1, w0, r0); <sup>1</sup> / <sub>3</sub> (r0, w1, r1); <sup>1</sup> / <sub>3</sub> (r1, w0); <sup>1</sup> / <sub>4</sub> (r0, |

|            | w0); $\hat{1}$ (r0, w1); $\hat{1}$ (r1, w1, w1); $\hat{1}$ (r1, w0); $\hat{1}$ (r0)}                                                                                                                                                                                                      |

| New March1 | $\{\hat{v}(w0); \hat{v}(r0, w0, r0, w0, w1); \hat{v}(r1, w0, w0); \hat{v}(r0, w0, w0, w1); \hat{v}(r1, w1, w1)\}$                                                                                                                                                                         |

| New March2 | $\{\hat{v}(w0); \hat{v}(r0, w0, r0, w0, w1); \hat{v}(r1, w1, w1); \hat{v}(r1, w1, w1, w1); \hat{v}(r1, w0, w0)\}$                                                                                                                                                                         |

| New March3 | $\{\uparrow(w0); \downarrow(r0,r0,w0,r0,w1); \uparrow(r1,r1,w1,r1,w0); \downarrow(r0,r0,w0,r0,w1); \downarrow(r1,r1,w1,r1,w1); \uparrow(r1) \}$                                                                                                                                           |

| New March4 | { \$\theta\$ (w0); \$\theta\$ (r0, r0, w0, r0, w1); \$\theta\$ (r1, w1, r1, w0); \$\theta\$ (r0, w0, r0, w1); \$\theta\$ (r1, w1, r1, w0, w0,                                                                                                                                             |

|            | r0); <sup>[1]</sup> (r0, w0, r0); <sup>[1]</sup> (r0, w0, r0); <sup>[1]</sup> (r0, w0); <sup>(1)</sup> (r0, w0, r0); <sup>(1)</sup> (r0, w0, r0); <sup>(1)</sup> (r0, w0); <sup>[1]</sup> (r0,                                                                                            |

|            | w0);                                                                                                                                                                                                                                                                                      |

Table 2.2: New Generated March Tests using Genetic Algorithm [37]

This technique reduces the testing power effectively in March test, but it performs this on individual memory whereas usually a large number of embedded memories have to be tested in parallel resulting in large peak power that may damage the chip.

#### 2.4 Generating Low Power March Tests using Particle Swarm Optimization

This technique is similar to the one described in the previous section. It aims to generate low power March tests with low power and high fault coverage using Particle Swarm Optimization (PSO) scheme. Actually PSO is a population based stochastic scheme which is used to find a solution and then finding the optima through iterations. As in genetic algorithm, new populations are generated from some initial population by applying a number of operations. Then, the one with the maximum fitness function is selected as optima. Usually, each particle consists of a sequence of read and write operations. Figure 2.4 illustrates the structure of PSO particle. The fitness function at kth generation of particle Pi equals to W1\* (Fraction of faults covered) + W2\*(Maximum power consumed by any particle till generation k)/ (Power consumed by the *March* test of particle *Pi* in generation k) +W3\*(Maximum number of continuous writes in any particle till generation k)/ (Number of contiguous writes for the March test of particle *Pi* in generation k)/ [38].

| $P_i = \{aw0 \ ur0w1 \ dr1w0\}$ | <ul> <li>0 - value is 0</li> <li>1 - value is 1</li> <li>w - write operation</li> <li>r - read operation</li> <li>u - increasing order of addressing</li> <li>d - decreasing order of addressing</li> <li>a - any order of addressing</li> </ul> |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### Figure 2.3: PSO Particle Structure [38]

The initial population in PSO scheme is generated by taking the Number Of Operations (NOP) of the March test as an input, then based on random variables, new particles are generated randomly. The fitness function is calculated for each of them. New particles are then generated using an operation called flip and the fitness function is calculated periodically. The particle with the best fitness function is selected as optima. More about PSO scheme can be found in appendix C.

Table 2.3 shows the newly generated March tests based on PSO scheme and their fault coverage and average power. It is obvious that this scheme is based mainly on the number of operations in the March test.

This algorithm reduces the testing power effectively through generating those low power March tests. But as in genetic algorithm, when a large number of embedded memories has to be tested simultaneously, then concurrent write operations will result in high peak power that may exceed the power constraint of the chip. Another drawback is that both this and genetic algorithm consider bit-oriented SRAM in their applications whereas most of the commonly used memories are word-oriented ones.

| Algorith<br>m | No<br>P | FC            | Power<br>(mW) | W | Alternate Test Generated                                                                                         |       | Power<br>(mW) |

|---------------|---------|---------------|---------------|---|------------------------------------------------------------------------------------------------------------------|-------|---------------|

| March A       | 15      | 01 60         | 0.260         | Α | aw0 ur0w1r1 ur1w0 ur0 dr0w1 dr1w0 ur0 uw1r1 dr1                                                                  | 96.59 | 0.230         |

| March A       | 15      | 81.68 0.368 B |               | В | aw0 ur0 dr0w1 ur1w0r0 dr0 uw1r1 dr1w0r0 ur0w1                                                                    | 95.01 | 0.230         |

| March M       | 16      | 82.73         | 0.046         | A | aw0 dr0w1 dr1 ur1w0r0 ur0w1 ur1w0w1 dr1 dr1w0 dr0                                                                | 96.59 | 0.245         |

| March M       | 10      | 82.73         | 0.246         | В | aw0 ur0 dw1r1 dr1w0 ur0 ur0w1 ur1w0r0 dr0 dr0w1r1                                                                | 96.16 | 0.219         |

| March B       | 17      | 81.77         | 0.333         | A | aw0 ur0w1 ur1 aw0 ur0w1 dr1w0r0 dr0w1 ur1w0w1w0 ur0                                                              | 97.07 | 0.283         |

| March D       | 17      | 01.77         | 0.555         | В | aw0 dr0 dw1r1 ur1 dr1w0r0 dr0w1r1 ur1w0 ur0w1r1 ur1                                                              | 93.57 | 0.210         |

| March G       | 23      | 89.45         | 0.299         | A | aw0 dr0w1w0r0 dr0w1 ur1w0r0w1 dr1w0 ur0w1 ur1w0r0 ur0 aw0 dr0w1 dr1                                              | 98.99 | 0.262         |

| March         | 25      | 07.45         | 0.299         | В | aw0 ur0w1 ur1 aw0 dr0 dr0w1 dr1 aw0 ur0w1r1 ur1w0r0 dr0w1r1 dr1w0r0 dr0                                          | 96.93 | 0.226         |

| ABL           | 37      | 94.72         | 0.252         | A | aw0 ur0w1r1w0r0 ur0w1r1 uw0r0 dr0w1 dr1w0r0 ur0 uw1 dr1 dw0r0w1r1<br>ur1w0 uw1r1 ur1w0 uv0 uv1 dr1w0r0 dr0w1 ur1 | 98.56 | 0.243         |

| ADL           | 57      | 24.72         | 0.252         | В | aw0 ur0w1r1w0r0 uw1r1 ur0w0 dr0w1r1 dr1w0r0 ur0 uw1 dr1 dw0r0w1r1<br>ur1w0 uw1r1 ur1w0 ur0 uw1 dr1w0r0 dr0w1 ur1 | 97.12 | 0.243         |

Table 2.3: New March Tests Based on PSO Scheme [38]

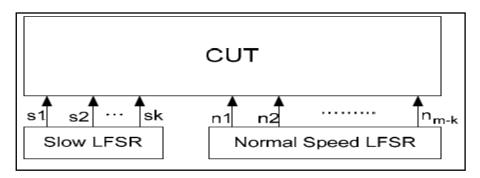

#### 2.5 Skew Scheme

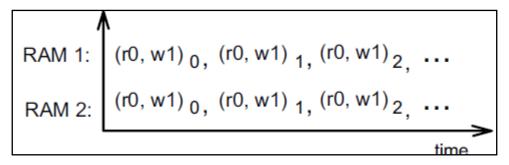

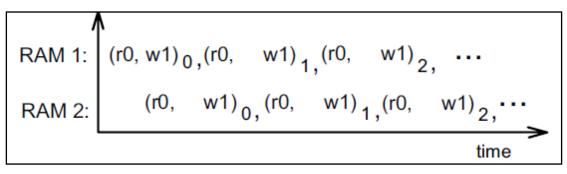

A SoC consists of a large number of embedded memories that have to be tested in parallel. When a memory testing algorithm, such as March C-, is applied on those memories, there will be concurrent write operations that will cause huge peak power that may damage the chip if it exceeds the power constraint. Figure 2.5 illustrates applying element M1 (R0,W1) in March C- algorithm on two SRAMs being tested in parallel.  $(r0,w1)_0$  means that these operations will be applied on cell 0. So write operation will be applied on two cells concurrently. If the SoC consists of 100 memories, then 100 concurrent write operations will be applied during parallel testing which is dangerous to the cell due to the high current of write operation if compared with read operation.

Figure 2.4: Applying element M1 of March C- on two SRAMs

The skew scheme was found in order to provide a good management for parallel testing of embedded memories. This is done by adding one clock cycle skew when testing two embedded memories to ensure that there will be no concurrent write operations. Figure 2.6 illustrates applying skew algorithm when element M1 of March C- algorithm is applied on two SRAMs being tested in parallel. Let P(R) and P(W) denotes read power and write power respectively. In case of parallel testing without any skew, as shown in figure 2.5, peak power will 2\*P(W) whereas it will be P(R)+P(W) when skew algorithm is applied as shown in figure 2.6. It is important to remember that always P(R) < P(W) [39].

Figure 2.5: Skew Scheme [39]

In general, If N identical memories have to be tested in parallel, and grouped into two clusters such that the memories in each cluster will be tested in parallel, then, scheduling read and write operations as shown in Figure 2.6 will result in a peak power reduction from N\*P(W) to (N/2)\*(P(W)+P(R)).

The main advantage of skew scheme is that it reduces the peak power effectively with just one additional clock cycle in the testing time. Nevertheless, if the power constraint of the chip is low, then skew scheme may be insufficient in reducing peak power since the memories in each cluster will be tested in parallel and may exceed this constraint.

#### 2.6 Power Constrained Embedded Memory BIST Architecture

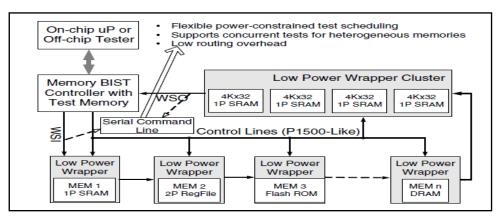

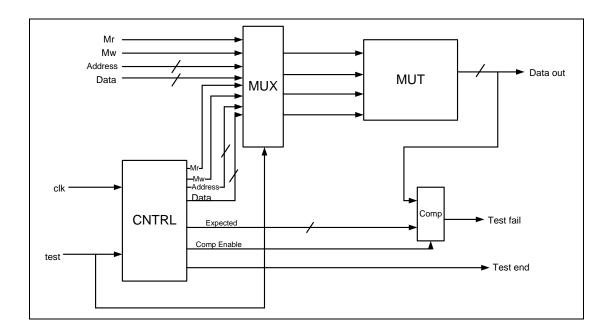

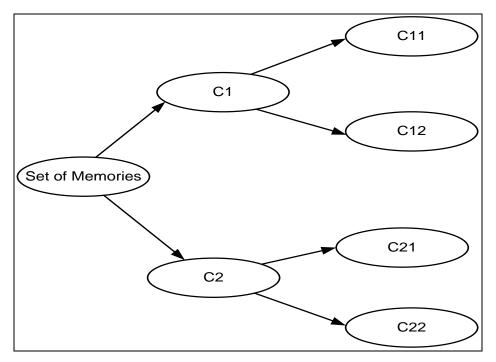

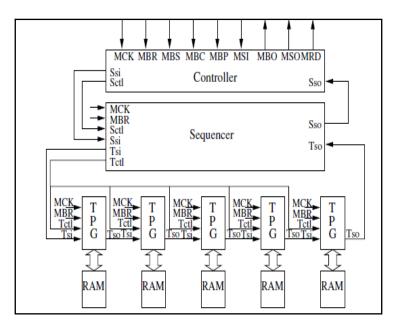

A good architecture was developed for MBIST in order to reduce the testing power and routing in connections. As shown in figure 2.7, this architecture consists of three main parts [40]:

- 1. MBIST controller in which the test program is stored and it starts the test after receiving a special command from upper level controller.

- 2. Low power MBIST wrapper which can be considered as the test pattern generator for the MUT and it is triggered by the controller to apply patterns.

3. Interconnections between controller and wrappers which is serial in order to reduce the routing complexity.

Figure 2.6: Power-Constrained MBIST Architecture [40]

Usually, MBIST controller sends commands to different wrappers that start applying testing patterns on the memories that have to be tested. Each wrapper uses gray code address generator in order to reduce the signal activities during testing. This generator can be up or down gray code counter. Each wrapper can be used to apply patterns on a single memory. Figure 2.8 illustrates the structure of address generator used in wrapper [40].

This architecture doesn't provide a management of parallel testing, since although the switching activity is reduced, parallel testing will result in abrupt increase in the peak power.

Figure 2.7: Wrapper Address Generator [40]

#### 2.7 Contribution of the Work Presented in this Thesis

This dissertation introduces a number of techniques for reducing testing power of embedded SRAMs in SoC. These techniques aim to enhance some of the algorithms described in this chapter to overcome their drawbacks.

In chapter 3, low power and low hardware area address generator is suggested in order to be used for Zero-One algorithm which is used for testing personal devices. So the switching activity in the address decoder is reduced with little overhead in hardware area. Then, the test is reordered so that the write drivers switching activity is reduced.

In chapter 4, an enhancement is applied on March tests for word oriented memories in order to reduce their peak and average power. Finally, a management of parallel testing of embedded memories is proposed in chapter 5. This is done by applying a new scheme which improves the skew scheme effectively.

The work presented in chapters 4 and 5 was accepted for publication in the IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT 2011) that will be held in 3-5 October, 2011 in Vancouver, Canada. Another paper about the contribution presented in chapter 3 is prepared to be submitted for another conference.

# CHAPTER 3

#### Low Power Zero-One Testing

#### 3.1 Overview

Stuck- at faults can be considered as the most common types of faults in SRAM cells. Usually, embedded memories of personal and mobile devices such as mobile phones and digital cameras are tested mainly for this type of faults. Actually, this is done during manufacturing and even in on-line testing, in which memory is tested when it is used in the application [18].

As mentioned in chapter 1, Zero-One algorithm is used for detecting stuck-at faults. This algorithm needs to be enhanced in order to reduce the power consumed during testing since power is a crucial factor for mobile devices especially if on-line testing is being applied.

This chapter introduces an enhancement of Zero-One algorithm in order to reduce the power consumed during testing. This enhancement consists of two main parts:

- 1. Selecting a low power address generator to reduce the switching activity in address decoder.

- 2. Reordering the Zero-One pattern so that total switching activity is minimized.

Section 3.2 describes the used MBIST architecture and address generators. Section 3.3 reorders Zero-One testing pattern so that total switching activity is minimized. Section 3.4 reports and analyzes obtained results while section 3.5 concludes this chapter.

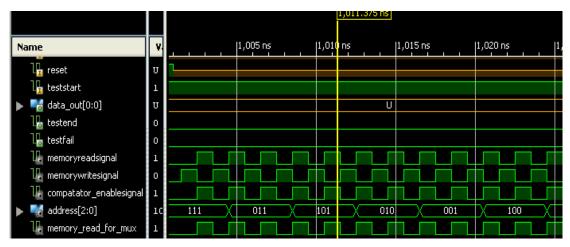

#### 3.2 MBIST Architecture and Address Generators

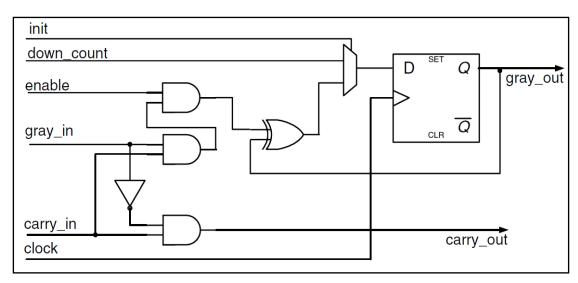

In MBIST, the BIST engine generates a number of testing vectors that are applied on MUT. Each vector consists of address that has to be accessed, data background that has to be written, and control signal to determine whether a read or a write operation has to be applied. Figure 3.1 shows the design for MBIST used in this chapter. Basically, the BIST engine (controller) provides mr and mw signal for read and write operations respectively. It also generates the address that has to be accessed and the data that will be written to MUT in case of write operation. If the operation is read, then the expected data to be read will be sent to the comparator that compares between this data with the output of MUT after read operation. The Mux has the test signal as its selection line in order to determine whether the system is in the functional mode or in the testing mode. In general, if the system is in the testing mode, then the patterns sent by BIST controller will be applied to the memory while the data coming from microprocessor will be applied if the system is in the normal mode. Finally, the comparator compares in parallel the data read from memory with the expected data; if these values are different, then the test fail signal will be activated indicating that the MUT is faulty. The test continues until the test end signal is activated by the BIST controller. More about building MBIST systems can be found in [41].

One of the possible enhancements for Zero-One pattern is to exploit the fact that during testing, the order of addresses generated is not important. For this reason, a low power and lower hardware area address generator has to be used. Since using a counter entails a large overhead in the hardware area, LFSR is usually used for this purpose [28]. As described in section 1.3, with a little hardware area and with the appropriate selection of XOR gate location, LFSR can generate all the possible addresses except the zero's address which can be generated using a simple circuit. This will not affect the fault coverage since all locations will be generated and tested.

Although LFSR occupies a low hardware area, there is a low correlation between the addresses generated. This causes a high switching activity in the address decoder which increases the heat dissipated during testing. Thus, other types of LFSR were developed in order to reduce the switching activity in the vectors generated. These LFSRs are used for testing combinational and sequential circuits, but they were not used for testing memories. Hence, these LFSRs were implemented, simulated, and then compared with each others in terms of their switching activity in order to find the best one to be used as an address generator when testing SRAMs for stuck-at faults. The following sections provide a brief description about these types of LFSR.

Figure 3.1: Used MBIST Architecture

#### 3.2.1 Bit-Swapping LFSR (BS-LFSR)

In this type, the LFSR structure is modified to apply swapping between the neighboring bits. The last bit is the selection line for the swapping process. If the last bit is 0, then swapping is performed between neighboring flip flops, otherwise, nothing is changed. As shown in figure 3.2, just a number of multiplexers have to be used to allow swapping. For example, if a 3-bit LFSR has to be used, then the generated vectors using normal LFSR (such as the one shown in figure 1.11) and BS-LFSR are shown in table 3.1. So each vector generated by normal LFSR is checked to see whether it has to be swapped or not. It was proven that BS-LFSR reduces the switching activity in the inputs of the CUT about 25% [42].

Figure 3.2: BS-LFSR [42]

| Swapped Vector |

|----------------|

| 111            |

| 011            |

| 101            |

| 101            |

| 001            |

| 010            |

| 110            |

| 111            |

|                |

Table 3.1: Normal and BS- LFSR Vectors

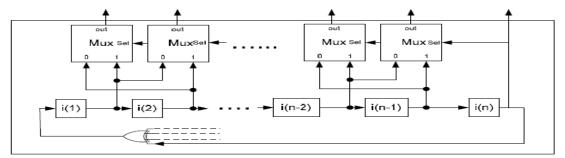

#### 3.2.2 Dual Speed LFSR (DS-LFSR)

This LFSR is commonly used in testing since it reduces the switching activity effectively. Instead of using one LFSR, two LFSRs are used: slow speed LFSR and normal speed LFSR. The slow-speed LFSR is driven by a slow clock whose speed is a fraction of the clock that drives the normal-speed LFSR. Figure 3.3 illustrate this type of LFSR. When the normal-speed LFSR finishes all its vectors, the slow-speed LFSR clock is triggered [43].

Figure 3.3: DS-LFSR [43]

The main feature of DS-LFSR is that it reduces the frequency of transitions in the circuit inputs that are driven by the slow-speed LFSR. So the total number of switching activities is reduced.

#### 3.2.3 Bipartite LFSR

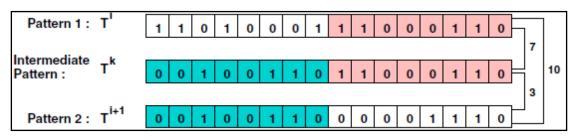

This LFSR is based on reducing the switching activity between two consecutive patterns through combining the second half of the current vector with the first half of the next vector into an intermediate vector. As shown in figure 3.4, the switching activity is divided into two stages [44].

Figure 3.4: Intermediate Pattern Generation in Bipartite LFSR [44]

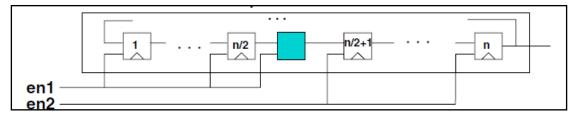

Bipartite LFSR can be implemented simply by dividing the LFSR into two halves so that when one half is working, the other half is idle. Actually two enable signals are required (en1, en2) as shown in figure 3.5. When en1en2=10, then the first half is working while when en1en2=01, then the second half is working. An intermediate flip flop is added to store the value of n/2th flip flop when the first half is active and sends it value to (n/2+1)th flip flop when the second half becomes active [44].

Figure 3.5: Bipartite LFSR Architecture [44]

Bipartite LFSR reduces instantaneous power, but for average power, it will be the same if all vectors are generated since it only divides the switching activity in two parts (for example from 10 to 7 and 3 as shown in figure 3.4). Another disadvantage is that if this generator was used for the same testing time of normal LFSR, then some addresses will be duplicated while others will not be generated, and this will affect the fault coverage of the test.

#### 3.3 Detecting Stuck-at Fault Patterns

In order to detect stuck-at faults, Zero-One pattern writes zero to all memory locations, then it reads zero from all these locations so that stuck-at one cells are detected. After that, one is written to all cells and then read to detect stuck-at zero cells. As mentioned in section 2.1, this pattern causes a high switching activity in the address decoder since all addresses will be generated four times and in case LFSR is being used, there will be huge switching activity, thus, the technique proposed in section 2.1 suggests to modify Zero-One pattern from  $\{\uparrow(W0); \uparrow(R0); \uparrow(W1); \uparrow(R1)\}$  to  $\{\uparrow(W0,R0,W1,R1)\}$ , so that all operations are applied on one cell then moving to the next cell. This will reduce the switching activity in the address decoder since the addresses will be generated just one time. To make it easier, the original Zero-One pattern will be called **pattern 1** while the later one will be called **pattern 2.** Switching activity of pattern 1 (SA<sub>p1</sub>) can be represented in (3.1)

$$SA_{p1} = 4 * SA_{add} + p \tag{3.1}$$

Where SA<sub>add</sub> is the address decoder switching activity and p is the word length of the MUT. Although pattern 2 reduces the switching activity in the address decoder, it entails a problem in the switching activity in the data bus since most of the memories used in reality are word oriented memories. For example, if the word length of the MUT is 8bits, then using pattern 2 will result in huge switching activity in the data bus since when each location has to be accessed, such as the second location, the data bus will have 16 transitions (1111111) $\rightarrow$ 00000000 $\rightarrow$ 11111111). Higher word lengths will result in higher switching activities. Switching activity of pattern 2 (SA<sub>p2</sub>) is represented by (3.2)

$$SA_{p2} = SA_{add} + p * (2N - 1)$$

(3.2)

Where N is the number of memory locations (words) in the MUT. Note that in each word, there will be 2p transitions from ones to zeros and then from zeros to ones except the first location which contains p transitions from zeros to ones (if it is initially assumed to contain zeros). It is obvious that pattern 2 has a bad impact on data bus switching activity since it is proportional to the word length and the number of locations in the MUT.

. To reduce switching activity, there should be some optimization between the address bus switching activity and data bus switching activity. First of all, the lowest power address generator has to be selected, and then, a suitable pattern has to be

applied so that there is no excessive power consumed either in the address decoder or in the data bus. By this way, Zero-One pattern can be modified to be { $\uparrow(W0,R0)$ ;  $\uparrow(W1,R1)$ } and let this pattern called **pattern 3.** So when applying this pattern, the data bus will contain one switching activity in each of its lines whereas the test goes through the addresses two times. Switching activity of pattern 3 (SA<sub>p3</sub>) is represented by (3.3).

$$SA_{p3} = 2 * SA_{add} + p \tag{3.3}$$